# 256K x 16-bit 3.3V Asynchronous Magnetoresistive RAM

# **Datasheet**

#### **Features**

- Single 3.3V Power Supply

- Industrial Temperature Range (-40°C to 110°C) and Military Temperature Range (-55°C to 125°C)

- Symmetrical High-speed Read and Write with Fast Access Time (35 ns)

- Flexible Data Bus Control: 8 bit or 16 bit Access

- Equal Address and Chip-enable Access Times

- Automatic Data Protection with Low-voltage Inhibit Circuitry to Prevent Writes on Power Loss

- All Inputs and Outputs are Transistor-transistor Logic (TTL) Compatible

- Fully Static Operation

- Full Nonvolatile Operation with 20 Years Minimum Data Retention

### Introduction

The EV2A16A is a 4,194,304-bit magnetoresistive random access memory (MRAM) device organized as 262,144 words of 16 bits. The EV2A16A is equipped with chip enable (E), write enable (W), and output enable (G) pins, allowing for significant system design flexibility without bus contention. Because the EV2A16A has separate byte-enable controls (LB and UB), individual bytes can be written and read.

MRAM is a nonvolatile memory technology that protects data in the event of power loss and does not require periodic refreshing. The EV2A16A is the ideal memory solution for applications that must permanently store and retrieve critical data quickly.

The EV2A16A is available in a 400-mil, 44-lead plastic small-outline TSOP type-II package RoHS compliant (MSL3 according to Jedec standard) with an industry-standard center power and ground SRAM pinout.

The EV2A16A is available in Industrial (-40°C to 110°C) and Military (-55°C to +125°C) temperature ranges.

Visit our website: www.e2v.com for the latest version of the datasheet

e2v semiconductors SAS 2015 0918F-HIREL-07/15

# 1. Device Pin Assignment

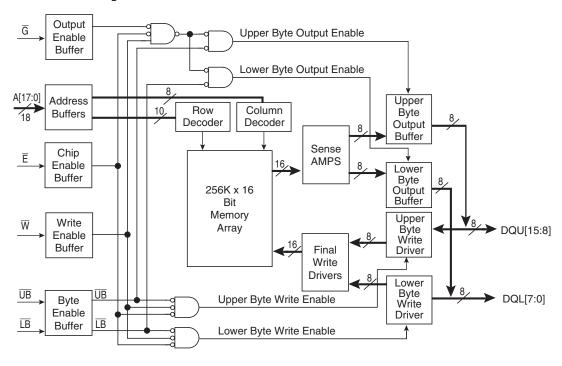

Figure 1-1. Block Diagram

**Table 1-1.** Pin Functions

| Signal Name     | Function          |

|-----------------|-------------------|

| А               | Address Input     |

| Ē               | Chip Enable       |

| $\overline{w}$  | Write Enable      |

| G               | Output Enable     |

| UB              | Upper Byte Enable |

| LB              | Lower Byte Enable |

| DQ              | Data I/O          |

| V <sub>DD</sub> | Power Supply      |

| V <sub>SS</sub> | Ground            |

| DC              | Do Not Connect    |

| NC              | No Connection     |

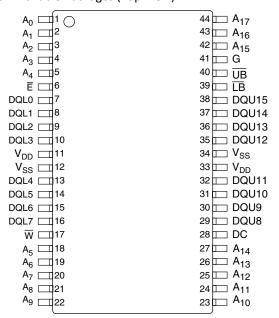

Figure 1-2. Pin Diagrams for Available Packages (Top View)

44-Pin TSOP Type2

**Table 1-2.** Operating Modes

| E <sup>(1)</sup> | <b>G</b> <sup>(1)</sup> | W <sup>(1)</sup> | LB <sup>(1)</sup> | UB <sup>(1)</sup> | Mode             | V <sub>DD</sub> Current             | DQL[7:0] <sup>(2)</sup> | DQU[15:8] <sup>(2)</sup> |

|------------------|-------------------------|------------------|-------------------|-------------------|------------------|-------------------------------------|-------------------------|--------------------------|

| Н                | Х                       | Х                | Х                 | Х                 | Not selected     | I <sub>SB1</sub> , I <sub>SB2</sub> | Hi-Z                    | Hi-Z                     |

| L                | Н                       | Н                | Х                 | Х                 | Output disabled  | I <sub>DDR</sub>                    | Hi-Z                    | Hi-Z                     |

| L                | Х                       | Х                | Н                 | Н                 | Output disabled  | I <sub>DDR</sub>                    | Hi-Z                    | Hi-Z                     |

| L                | L                       | Н                | L                 | Н                 | Lower Byte Read  | I <sub>DDR</sub>                    | D <sub>Out</sub>        | Hi-Z                     |

| L                | L                       | Н                | Н                 | L                 | Upper Byte Read  | I <sub>DDR</sub>                    | Hi-Z                    | D <sub>Out</sub>         |

| L                | L                       | Н                | L                 | L                 | Word Read        | I <sub>DDR</sub>                    | D <sub>Out</sub>        | D <sub>Out</sub>         |

| L                | Х                       | L                | L                 | Н                 | Lower Byte Write | I <sub>DDW</sub>                    | D <sub>in</sub>         | Hi-Z                     |

| L                | Х                       | L                | Н                 | L                 | Upper Byte Write | I <sub>DDW</sub>                    | Hi-Z                    | D <sub>in</sub>          |

| L                | Х                       | L                | L                 | L                 | Word Write       | I <sub>DDW</sub>                    | D <sub>in</sub>         | D <sub>in</sub>          |

Notes: 1. H = high, L = low, X = don't care

2. Hi-Z = high impedance

#### **Electrical Specifications** 2.

#### 2.1 **Absolute Maximum Ratings**

This device contains circuitry to protect the inputs against damage caused by high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage greater than maximum rated voltages to these high-impedance (Hi-Z) circuits.

The device also contains protection against external magnetic fields. Precautions should be taken to avoid application of any magnetic field more intense than the maximum field intensity specified in the maximum ratings.

**Table 2-1.** Absolute Maximum Ratings(1)

| Symbol                 | Parameter                                     | Temp Range           | Package  | Value                         | Unit |

|------------------------|-----------------------------------------------|----------------------|----------|-------------------------------|------|

| $V_{DD}$               | Supply voltage <sup>(2)</sup>                 | -                    | _        | -0.5 to 4.0                   | V    |

| V <sub>IN</sub>        | Voltage on any pin (2)                        | _                    | _        | -0.5 to V <sub>DD</sub> + 0.5 | V    |

| I <sub>OUT</sub>       | Output current per pin                        | _                    | _        | ±20                           | mA   |

| $P_{D}$                | Package power dissipation (3)                 | _                    | Note (3) | 0.600                         | W    |

| <del>-</del>           |                                               | Industrial           | _        | -40 to 110                    | °C   |

| T <sub>BIAS</sub>      | Temperature under bias                        | Military             | _        | -55 to 125                    |      |

| T <sub>stg</sub>       | Storage Temperature                           | _                    | _        | -65 to 150                    | °C   |

| T <sub>Lead</sub>      | Lead temperature during solder (3 minute max) | -                    | -        | 260                           | °C   |

| H <sub>max_write</sub> | Maximum magnetic field during write           | Industrial, Military | TSOP2    | 2000                          | A/m  |

| H <sub>max_read</sub>  | Maximum magnetic field during read or standby | Industrial, Military | TSOP2    | 8000                          | A/m  |

Notes:

- 1. Permanent device damage may occur if absolute maximum ratings are exceeded. Functional operation should be restricted to recommended operating conditions. Exposure to excessive voltages or magnetic fields could affect device reliability.

- 2. All voltages are referenced to V<sub>SS</sub>.

- 3. Power dissipation capability depends on package characteristics and use environment.

**Table 2-2. Operating Conditions**

| Parameter                           | Symbol          | Min                 | Typical | Max                                  | Unit |

|-------------------------------------|-----------------|---------------------|---------|--------------------------------------|------|

| Power supply voltage <sup>(1)</sup> | V <sub>DD</sub> | 3.0 <sup>(1)</sup>  | 3.3     | 3.6                                  | V    |

| Write inhibit voltage               | V <sub>wi</sub> | 2.5                 | 2.7     | 3.0 <sup>(1)</sup>                   | V    |

| Input high voltage                  | V <sub>IH</sub> | 2.2                 | -       | V <sub>DD</sub> + 0.3 <sup>(2)</sup> | V    |

| Input low voltage                   | V <sub>IL</sub> | -0.5 <sup>(3)</sup> | -       | 0.8                                  | V    |

| Operating temperature               | Tcase           | -40<br>-55          |         | +110<br>+125                         | °C   |

- Notes: 1. There is a 2 ms startup time once V<sub>DD</sub> exceeds V<sub>DD</sub>, (max). See **Power Up and Power Down Sequencing** below.

- 2.  $V_{IH}(max) = V_{DD} + 0.3 V_{DC}$ ;  $V_{IH}(max) = V_{DD} + 2.0 V_{AC}$  (pulse width  $\leq 10$  ns) for  $I \leq 20.0$  mA.

- 3.  $V_{II}(min) = -0.5 V_{DC}$ ;  $V_{II}(min) = -2.0 V_{AC}$  (pulse width  $\leq 10$  ns) for  $I \leq 20.0$  mA.

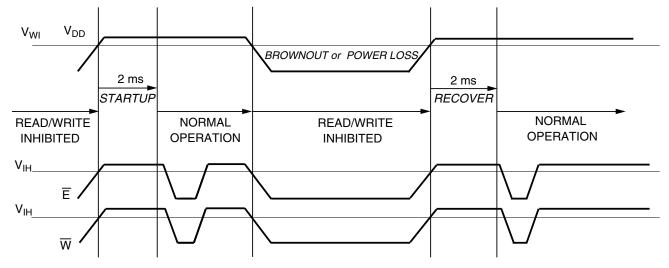

## 2.2 Power-up and Power-down Sequencing

The MRAM is protected from write operations whenever  $V_{DD}$  is less than  $V_{WI}$ . As soon as  $V_{DD}$  exceeds  $V_{DD}$  (min), there is a startup time of 2 ms before read or write operations can start. This time allows memory power supplies to stabilize.

The  $\overline{E}$  and  $\overline{W}$  control signals should track  $V_{DD}$  on power up to  $V_{DD} - 0.2 \text{ V}$  or  $V_{IH}$  (whichever is lower) and remain high for the startup time. In most systems, this means that these signals should be pulled up with a resistor so that signal remains high if the driving signal is Hi-Z during power up. Any logic that drives E and W should hold the signals high with a power-on reset signal for longer than the startup time.

During power loss or brownout where  $V_{DD}$  goes below  $V_{WI}$ , writes are protected and a startup time must be observed when power returns above  $V_{DD}$ (min).

Figure 2-1. Power Up and Power Down Diagram

**Table 2-3.** DC Characteristics

| Parameter                                                                      | Symbol              | Min                          | Typical | Max                          | Unit |

|--------------------------------------------------------------------------------|---------------------|------------------------------|---------|------------------------------|------|

| Input leakage current                                                          | $I_{lkg(l)}$        | -                            | -       | ±1                           | μΑ   |

| Output leakage current                                                         | I <sub>Ikg(O)</sub> | -                            | -       | ±1                           | μΑ   |

| Output low voltage<br>(I <sub>OL</sub> = +4 mA)<br>(I <sub>OL</sub> = +100 μA) | V <sub>OL</sub>     | -                            | -       | 0.4<br>V <sub>SS</sub> + 0.2 | >    |

| Output high voltage $(I_{OH} = -4 \text{ mA})$ $(I_{OH} = -100 \mu\text{A})$   | V <sub>OH</sub>     | 2.4<br>V <sub>DD</sub> – 0.2 | ı       | ı                            | ٧    |

**Table 2-4.** Power Supply Characteristics

| Parameter                                                                                                                                                          | Symbol           | Typical    | Max        | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|------------|------|

| AC active supply current – read modes <sup>(1)</sup> (I <sub>OUT</sub> = 0 mA, V <sub>DD</sub> = max)                                                              | I <sub>DDR</sub> | 55         | 80         | mA   |

| AC active supply current – write modes <sup>(1)</sup> (V <sub>DD</sub> = max) Industrial Grade Military Grade                                                      | I <sub>DDW</sub> | 105<br>105 | 165<br>165 | mA   |

| AC standby current $(V_{DD} = max, \overline{E} = V_{IH})$ no other restrictions on other inputs                                                                   | I <sub>SB1</sub> | 18         | 28         | mA   |

| CMOS standby current $(\overline{E} \geq V_{DD} - 0.2V \text{ and } V_{In} \leq V_{SS} + 0.2V \text{ or } \geq V_{DD} - 0.2V)$ $(V_{DD} = max, f = 0 \text{ MHz})$ | I <sub>SB2</sub> | 9          | 12         | mA   |

Note: 1. All active current measurements are measured with one address transition per cycle and at minimum cycle time.

# 3. Timing Specifications

**Table 3-1.** Capacitance<sup>(1)</sup>

| Parameter                 | Symbol           | Typical | Max | Unit |

|---------------------------|------------------|---------|-----|------|

| Address input capacitance | C <sub>In</sub>  | -       | 6   | pF   |

| Control input capacitance | C <sub>In</sub>  | -       | 6   | pF   |

| Input/Output capacitance  | C <sub>I/O</sub> | -       | 8   | pF   |

Note: 1. f = 1.0 MHz, dV = 3.0V,  $T_A = 25$ °C, periodically sampled rather than 100% tested.

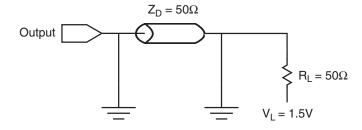

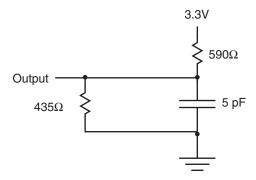

Table 3-2.AC Measurement Conditions

| Parameter                                         | Value          | Unit |  |

|---------------------------------------------------|----------------|------|--|

| Logic input timing measurement reference level    | 1.5V           | V    |  |

| Logic output timing measurement reference level   | 1.5V           | V    |  |

| Logic input pulse levels                          | 0 or 3.0 V     | ٧    |  |

| Input rise/fall time                              | 2              | ns   |  |

| Output load for low and high impedance parameters | See Figure 3-1 |      |  |

| Output load for all other timing parameters       | See Figure 3-2 |      |  |

Figure 3-1. Output Load Test Low and High

Figure 3-2. Output Load Test All Others

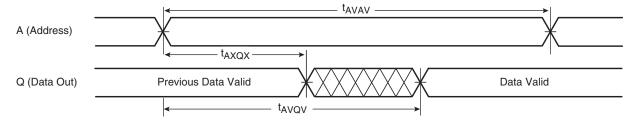

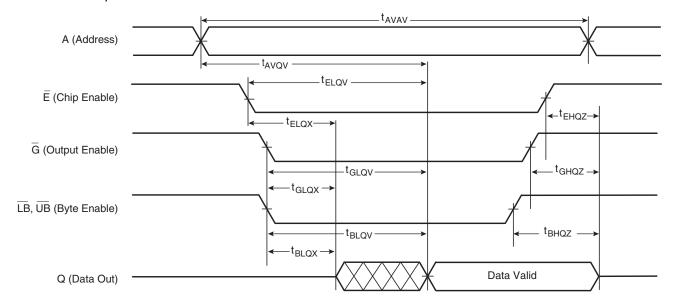

**Table 3-3.** Read Cycle Timing<sup>(1)</sup>

| Parameter                                         | Symbol            | Min | Max | Unit |

|---------------------------------------------------|-------------------|-----|-----|------|

| Read cycle time                                   | t <sub>AVAV</sub> | 35  | -   | ns   |

| Address access time                               | t <sub>AVQV</sub> | -   | 35  | ns   |

| Enable access time <sup>(2)</sup>                 | t <sub>ELQV</sub> | -   | 35  | ns   |

| Output enable access time                         | t <sub>GLQV</sub> | -   | 15  | ns   |

| Byte enable access time                           | t <sub>BLQV</sub> | _   | 15  | ns   |

| Output hold from address change                   | t <sub>AXQX</sub> | 3   | -   | ns   |

| Enable low to output active <sup>(3)</sup>        | t <sub>ELQX</sub> | 3   | -   | ns   |

| Output enable low to output active <sup>(3)</sup> | t <sub>GLQX</sub> | 0   | _   | ns   |

| Byte enable low to output active <sup>(3)</sup>   | t <sub>BLQX</sub> | 0   | -   | ns   |

| Enable high to output Hi-Z <sup>(3)</sup>         | t <sub>EHQZ</sub> | 0   | 15  | ns   |

| Output enable high to output Hi-Z <sup>(3)</sup>  | t <sub>GHQZ</sub> | 0   | 10  | ns   |

| Byte high to output Hi-Z <sup>(3)</sup>           | t <sub>BHQZ</sub> | 0   | 10  | ns   |

Notes: 1.  $\overline{W}$  is high for read cycle. Power supplies must be properly grounded and decoupled, and bus contention conditions must be minimized or eliminated during read or write cycles.

- 2. Addresses valid before or at the same time  $\overline{E}$  goes low.

- 3. This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage.

Figure 3-3. Read Cycle 1

Note: Device is continuously selected ( $\overline{E} \le V_{IL}, \ \overline{G} \le V_{IL}$ )

Figure 3-4. Read Cycle 2

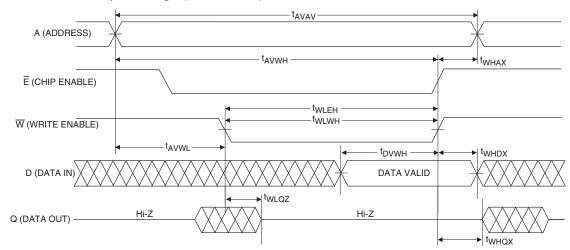

**Table 3-4.** Write Cycle Timing 1  $(\overline{W} \text{ Controlled})^{(1)}$

| Parameter                                  | Symbol                                 | Min | Max | Unit |

|--------------------------------------------|----------------------------------------|-----|-----|------|

| Write cycle time <sup>(2)</sup>            | t <sub>AVAV</sub>                      | 35  | _   | ns   |

| Address set-up time                        | t <sub>AVWL</sub>                      | 0   | _   | ns   |

| Address valid to end of write (G high)     | t <sub>AVWH</sub>                      | 18  | _   | ns   |

| Address valid to end of write (G low)      | t <sub>AVWH</sub>                      | 20  | _   | ns   |

| Write pulse width (G high)                 | t <sub>WLWH</sub> /t <sub>WLEH</sub>   | 15  | -   | ns   |

| Write pulse width (G low)                  | t <sub>WLWH</sub><br>t <sub>WLEH</sub> | 15  | _   | ns   |

| Data valid to end of write                 | t <sub>DVWH</sub>                      | 10  | _   | ns   |

| Data hold time                             | t <sub>whdx</sub>                      | 0   | _   | ns   |

| Write low to data Hi-Z <sup>(3)</sup>      | t <sub>wLQZ</sub>                      | 0   | 12  | ns   |

| Write high to output active <sup>(3)</sup> | t <sub>whqx</sub>                      | 3   | _   | ns   |

| Write recovery time                        | t <sub>WHAX</sub>                      | 12  | _   | ns   |

Notes:

- 1. All write occurs during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W, E or UB/LB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

- 2. All write cycle timings are referenced from the last valid address to the first transition address.

- 3. This parameter is sampled and not 100% tested. Transition is measured ±200 mV from the steady-state voltage. At any given voltage or temperate, t<sub>WLQZ</sub>(max) < t<sub>WHQX</sub>(min)

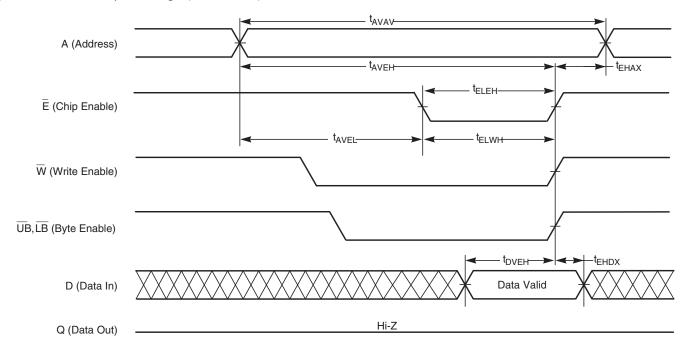

**Figure 3-5.** Write Cycle Timing 1 ( $\overline{W}$  Controlled)<sup>(1)</sup>

**Table 3-5.** Write Cycle Timing 2 ( $\overline{E}$  Controlled)<sup>(1)</sup>

| Parameter                                                   | Symbol                                 | Min | Мах | Unit |

|-------------------------------------------------------------|----------------------------------------|-----|-----|------|

| Write cycle time <sup>(2)</sup>                             | t <sub>AVAV</sub>                      | 35  | _   | ns   |

| Address set-up time                                         | t <sub>AVEL</sub>                      | 0   | _   | ns   |

| Address valid to end of write (G high)                      | t <sub>AVEH</sub>                      | 18  | _   | ns   |

| Address valid to end of write (G low)                       | t <sub>AVEH</sub>                      | 20  | _   | ns   |

| Enable to end of write (G high)                             | t <sub>eleh</sub><br>t <sub>elwh</sub> | 15  | -   | ns   |

| Enable to end of write ( $\overline{G}$ low) <sup>(3)</sup> | t <sub>eleh</sub><br>t <sub>elwh</sub> | 15  | -   | ns   |

| Data valid to end of write                                  | t <sub>DVEH</sub>                      | 10  | _   | ns   |

| Data hold time                                              | t <sub>EHDX</sub>                      | 0   | _   | ns   |

| Write recovery time                                         | t <sub>EHAX</sub>                      | 12  | _   | ns   |

Notes:

- 1. All write occurs during the overlap of E low and W low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If G goes low at the same time or after W goes low, the output will remain in a high impedance state. After W, E or UB/LB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

- 2. All write cycle timings are referenced from the last valid address to the first transition address.

- 3. If E goes low at the same time or after W goes low, the output will remain in a high-impedance state. If E goes high at the same time or before W goes high, the output will remain in a high-impedance state.

Write Cycle Timing 2 (E Controlled) Figure 3-6.

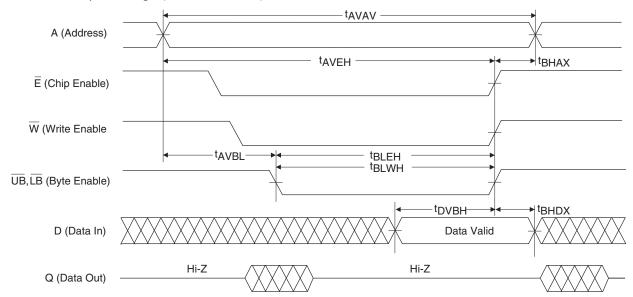

Write Cycle Timing 3 (LB/UB Controlled)(1) **Table 3-6.**

| Parameter                                                  | Symbol                                 | Min | Max | Unit |

|------------------------------------------------------------|----------------------------------------|-----|-----|------|

| Write cycle time <sup>(2)</sup>                            | t <sub>AVAV</sub>                      | 35  | ı   | ns   |

| Address set-up time                                        | t <sub>AVBL</sub>                      | 0   | ı   | ns   |

| Address valid to end of write ( $\overline{G}$ high)       | t <sub>AVBH</sub>                      | 18  | ı   | ns   |

| Address valid to end of write $(\overline{G} \text{ low})$ | t <sub>AVBH</sub>                      | 20  | ı   | ns   |

| Write pulse width (G high)                                 | t <sub>BLEH</sub><br>t <sub>BLWH</sub> | 15  | -   | ns   |

| Write pulse width (G low)                                  | t <sub>BLEH</sub><br>t <sub>BLWH</sub> | 15  | -   | ns   |

| Data valid to end of write                                 | t <sub>DVBH</sub>                      | 10  | -   | ns   |

| Data hold time                                             | t <sub>BHDX</sub>                      | 0   | -   | ns   |

| Write recovery time                                        | t <sub>BHAX</sub>                      | 12  | -   | ns   |

- Notes: 1. All write occurs during the overlap of  $\overline{E}$  low and  $\overline{W}$  low. Power supplies must be properly grounded and decoupled and bus contention conditions must be minimized or eliminated during read and write cycles. If  $\overline{G}$  goes low at the same time or after  $\overline{W}$  goes low, the output will remain in a high impedance state. After W, F or LB/UB has been brought high, the signal must remain in steady-state high for a minimum of 2 ns. If both byte control signals are asserted, the two signals must have no more than 2 ns skew between them. The minimum time between E being asserted low in one cycle to E being asserted low in a subsequent cycle is the same as the minimum cycle time allowed for the device.

- 2. All write cycle timings are referenced from the last valid address to the first transition address.

Figure 3-7. Write Cycle Timing 3 ( $\overline{LB}/\overline{UB}$  Controlled)

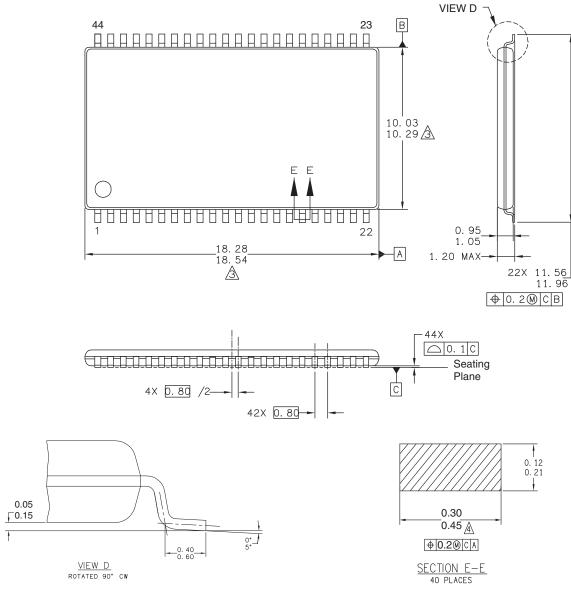

## 4. Mechanical Drawing

**Figure 4-1.** 44-TSOP2

#### **Print Version Not To Scale**

- 1. Dimensions and tolerances per ASME Y14.5M 1994.

- 2. Dimensions in Millimeters.

- ⚠ Dimensions do not include mold protrusion.

- Dimension does not include DAM bar protrusions.

DAM Bar protrusion shall not cause the lead width to exceed 0.58.

# 5. Ordering Information

This product is available in Industrial and Military temperature versions.

Figure 5-1. Ordering Information

| EV         | 2               | Α              | 16                   | Α         | Х                                    | N               | Υ                                | U           | 35           |

|------------|-----------------|----------------|----------------------|-----------|--------------------------------------|-----------------|----------------------------------|-------------|--------------|

|            | Density<br>Code | Memory<br>Type | I/O<br>Configuration | Revision  | Operating<br>Temperature<br>Range    | Package<br>Type | RoHS<br>compliance               | Upscreening | Timing Set   |

| e2v Prefix | 2 = 4 Mb        | A = async      | 16 = 16 bits         | A =180 mm | V = -40 to 110°C<br>M = -55 to 125°C | (N = TSOP II)   | Y: RoHS <sup>(2)</sup> compliant | U           | (35 = 35 ns) |

Notes: 1. For availability of the different versions, contact your local e2v sales office.

2. Lead finishing: pure tin (Sn 99,99%)

# 6. Document Revision History

Table 6-1 provides a revision history for this hardware specification.

**Table 6-1.** Document Revision History

| Rev. No | Date    | Substantive Change(s)                                                                                                                    |  |  |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0918F   | 07/2015 | Corrected error in Table 2-1 on page 4, "Storage Temperature"                                                                            |  |  |

| 0918E   | 02/2013 | Corrected error in Table 1-1, "Pin Functions," on page 2. Corrected Figure 3-1 on page 6.                                                |  |  |

| 0918D   | 06/2012 | Updated picture page 1.                                                                                                                  |  |  |

| 0918C   | 09/2010 | Updated Table 2-2 on page 4.                                                                                                             |  |  |

| 0918B   | 06/2009 | Add Section 2.2 "Power-up and Power-down Sequencing" on page 5. Correct Ioh spec to 100 $\mu$ A Correct AC test conditions.              |  |  |

| 0918A   | 12/2007 | Table 1-2: Changed I <sub>DDA</sub> to I <sub>DDR</sub> or I <sub>DDW</sub> Figure 5-1: Added RoHS compliance status in the part number. |  |  |

| 0918AX  | 11/2007 | Initial revision.                                                                                                                        |  |  |

#### How to reach us

Home page: www.e2v.com

**Sales and Support Offices:**

**EMEA and India: Regional sales Offices**

e2v

106 Waterhouse Lane Chelmsford

Essex CM1 2QU England

Tel: +44 (0)1245 493493

Fax: +44 (0)1245 492492

mailto: enquiries@e2v.com

e2v

16 Burospace

F-91572 Bièvres Cedex France

Tel: +33 (0) 16019 5500 Fax: +33 (0) 16019 5529

mailto: enquiries-fr@e2v.com

e2v - Germany and Austria only

106 Waterhouse Lane Chelmsford

Essex CM1 2QU England Tel: +44 (0)1245 493493 Fax: +44 (0)1245 453725

Americas

e2v inc

765 Sycamore Drive California 95035 USA Tel: +1 408 737 0992

Fax: +1 408 736 8708

mailto: enquiries-na@e2v.com

e2v inc

520 White Plains Road

Suite 450 Tarrytown, NY 10591 USA

Tel: +1 (914) 592 6050 or 1-800-342-5338,

Fax: +1 (914) 592-5148

mailto: enquiries-na@e2v.com

Asia Pacific

e2v

Unit A, 23/F, @Convoy No. 169 Electric Road

North Point Hong Kong

Telephone: +852 3679 364 8/9

Fax: +852 3583 1084

mailto: enquiries-ap@e2v.com

**Product Contact:**

e2v

4 Avenue de Rochepleine

BP 123 - 38521 Saint-Egrève Cedex

France

Tel: +33 (0)4 76 58 30 00

Hotline:

mailto: std-hotline@e2v.com

While e2v has taken care to ensure the accuracy of the information contained herein, it accepts no responsibility for the consequences of any use thereof and also reserves the right to change the specification of goods without prior notice. e2v accepts no liability beyond that set out in its standard conditions of sale in respect of infringement of third party patents arising from the use of tubes or other devices in accordance with information contained herein.

Users of e2v products are responsible for their own products and applications. e2v technologies does not assumes liability for application support and assistance. e2v technologies reserves the right to modify, make corrections, improvements and other changes to its products and services at any time and to discontinue any product without prior notice. Customers are advised to obtain the latest relevant information prior to placing orders.

e2v semiconductors SAS 2015 0918F-HIREL-07/15